- 地域連携外部ページTOP

- 研究者シーズ

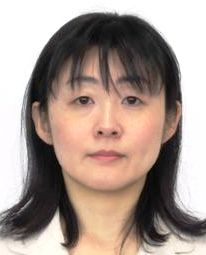

- 菅原 英子/ SUGAWARA Eiko

自律再構成ハードウェアシステムの構築

- 氏名

- 菅原 英子/ SUGAWARA Eiko

- ume56@akita-nct.ac.jp

- 職名

- 准教授

- 学位

- 博士(情報科学)

- 所属学会・協会

- 電子情報通信学会

- キーワード

- 自律再構成、故障補償、ディジタル回路設計

- 技術相談

提供可能技術 - ・ハードウェアシステムの故障補償

・FPGAを用いたディジタル回路の設計・実装

研究内容

自律的な故障補償が可能なハードウェアニューラルネットワークシステム

ニューラルネットワークはパターン認識やデータマイニングなど様々な場面で利用されている。一般にはソフトウェアシミュレーションにより実行されるが、ニューラルネットワークのハードウェア化(専用システム構築)は汎用計算機によるソフトウェアシミュレーションに比べ高速実行が可能になる、他機器への組み込みが容易になるなどの利点があり、研究・開発が行われている。ニューラルネットワークに限らず、ハードウェアシステムを設計する場合、現在の技術ではハードウェア上に発生する故障は避けられず、何らかの故障対策が必要不可欠である。本研究では、故障補償機構を組み込むことで外部の計算機を用いずに自律的に故障を検出・補償する階層型ニューラルネットワークシステムを提案し、ハードウェア化に適した階層型ニューラルネットワークの構成・実装法、自律的な故障補償を実現するための補償アルゴリズムやハードウェア構成法について研究をおこなっている。また、ニューラルネットワークを利用したパターン認識なども扱っている。

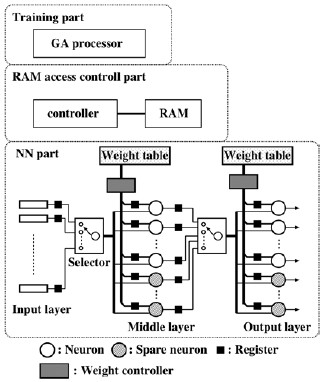

図1に提案するシステムの構成を示す。階層型ニューラルネットワークのハードウェアシステムとは、複数の演算素子が階層型のネットワークを形成する処理システムであり、演算素子(ニューロン)、メモリ(結合重み)、配線(ニューロン間結合)で構成される。故障補償手法として、予備回路を用いて故障箇所を物理的に切り離す冗長手法と、結合重みの更新によりネットワークから故障の影響を取り除く重み学習手法の二つがある。本システムでは、予備ニューロン回路による故障補償(冗長手法)とGA processorによる結合重みの更新(学習手法)を組み合わせた故障補償機構を階層型ニューラルネットワーク回路に組み込む。比較的少量の故障発生時には、故障箇所を中間層および出力層に配置した予備ニューロン回路に切り替えることにより、短時間で故障箇所を取り除くことができる。また、予備回路以上の故障が発生した場合には、故障ニューロンを除いたネットワーク構成での結合重みを再学習することで故障の影響を取り除くことができる。

図1 階層型ニューラルネットワークシステムの概要

提供可能な設備・機器

| 名称・型番(メーカー) | |

|---|---|

| FPGAボード(Xilinx社製FPGA搭載、東京エレクトロンデバイス他) | |